## www.thinkSRS.com

# **Gated Integrators and Boxcar Averagers**

SR250 — Gated integrator

- Gate widths from 2 ns to 15 μs (expandable to 150 μs)

- Internal rate generator

- Active baseline subtraction

- Shot-by-shot output

- Gate output for precise gate timing

- Average 1 to 10,000 samples

- DC to 20 kHz repetition rate

- Low jitter (<20 ps + 0.01 % of delay)

• SR250 ... \$2990 (U.S. list)

## SR250 Gated Integrator

The SR250 Gated Integrator is a versatile, high-speed NIM module designed to recover fast analog signals from noisy backgrounds.

The SR250 consists of a gate generator, a fast gated integrator, and exponential averaging circuitry. The gate generator, triggered internally or externally, provides an adjustable delay from a few nanoseconds to 100 ms before it generates a continuously adjustable gate with a width between 2 ns and 15  $\mu$ s. The gate delay can be set from the front panel or can be automatically scanned by applying a rear-panel control voltage. Scanning the gate allows the recovery of entire waveforms.

The fast gated integrator integrates the input signal during the gate. The output from the integrator is then normalized by the gate width to provide a voltage proportional to the average of the input signal during the sampling gate. This signal is further amplified and sampled by a low droop sample-and-hold amplifier, and output via a front-panel BNC connector. The last sample output allows for a shot-by-shot analysis of the

signal, and makes the instrument a particularly useful component in a computer data acquisition system.

## Triggering

The SR250 may be triggered internally or externally. The internal rate generator is continuously variable from 0.5 Hz to 20 kHz in nine ranges. The external trigger pulse may be as short as 5 ns, allowing the unit to be triggered with fast pulses from photodiodes and photomultipliers. Single shot and line triggering can also be selected.

## **Signal Inputs**

The sensitivity (Vin/Vout) of the instrument may be set from 1 V/V to 5 mV/V. If additional gain is required, the SR250 can be used with the SR240 preamplifier. The input is protected to 100 V and has a 1 M $\Omega$  input impedance. An input filter rejects unwanted signals before the input is sampled by the integrator. Unwanted DC input offsets are easily nulled with a 10-turn potentiometer.

phone: (408)744-9040 www.thinkSRS.com

## **Gate Timing**

The delay of the sample gate from the trigger is set by the delay multiplier and scale. The delay scale is multiplied by the setting on the 10-turn multiplier dial, allowing continuously adjustable delays from a few nanoseconds to 100 ms. The delay multiplier may also be changed from the rear-panel control voltage input, a useful feature in applications requiring a scanning gate. Zero to ten volts at this input overrides the front-panel 0 to  $10\times$  delay multiplier. Insertion delay from trigger to gate is only 25 ns, and gate-delay jitter is only 20 ps + 0.01 % of the full-scale delay.

The width of the sampling gate may be continuously adjusted from 2 ns to 15  $\mu$ s over eight width ranges. A simple modification of the unit allows gate widths of up to 150  $\mu$ s. The front-panel gate output provides a representation of the gate that can be overlayed with the signal on an oscilloscope to provide a precise display of the gate timing.

## **Signal Outputs**

A moving exponential average of 1 to 10,000 samples can be selected from the front panel. This traditional averaging technique is useful for pulling small signals from noisy backgrounds. In the case of a random white noise background, the signal-to-noise ratio increases by the square root of the number of samples in the average. This allows a S/N improvement of up to a factor of 100 using this technique alone. If no averaging is desired, or if averaging is to be performed on an external computer, the last sample output provides a voltage proportional to the average value of the input signal during the last gate period.

## **Average Reset**

The reset button sets the average output to zero. The average may also be reset by a rear-panel logic input. The average reset input will accept a TTL signal or a switch closure to ground to reset the moving average output.

## **Polarity Control and Active Baseline Subtraction**

The polarity of the last sample and averaged outputs is controlled by rear-panel toggle switches. Positive outputs can be selected for negative signals, and vice versa, allowing easy interfacing with unipolar analog to digital conversion systems. In addition to the traditional averaging modes, the SR250 possesses a unique Active Baseline Subtraction mode which allows you to actively cancel baseline drift. In the Active Baseline Subtraction mode, the SR250 is triggered at twice the source repetition rate. On alternate triggers, when the signal is not present, only the baseline is sampled and the SR250 inverts the polarity of the last sample output before it is added to the moving average. Thus, any baseline drift not associated with the source will be subtracted out.

## **Additional Outputs**

The signal input is passed on to the signal output by a length of coaxial cable for termination and for gate timing. It is delayed exactly 3.5 ns from the input and can be terminated to optimize either signal gain or response time. The gate output provides a pulse synchronized with the internal gate signal. The gate output is timed so that it can be overlayed with the signal output for precise adjustment of gate timing. The busy output provides a TTL timing pulse which is high while the unit is integrating, and goes low when the SR250 is ready to accept another trigger. These outputs help simplify experimental setup and troubleshooting.

SR250 rear panel

Ordering InformationSR250Gated integrator\$2990

phone: (408)744-9040 www.thinkSRS.com

## SR250 Specifications

| Trigger                                                        |                                                                                                                                                                                                                                    | Descents                                  | short circuit limit). Impedance $<1 \Omega$                                                                                                                                                                                 |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal trigger<br>Line trigger                               | 0.5 Hz to 20 kHz<br>The gate generator may be triggered                                                                                                                                                                            | Droop rate                                | When no ext. triggers are present,<br>droop rate is $<1$ % per minute<br>(1 to 30 samples), and $<0.01$ %                                                                                                                   |

| External trigger                                               | from AC line with adjustable phase.<br>1 M $\Omega$ input impedance. Trigger<br>threshold adjustable from 0.5 to 2 V.<br>Input protected to ±100 VDC.<br>Trigger pulse must be over threshold<br>for >5 ns with a rise time <1 µs. | Average polarity and baseline subtraction | per minute (100 to 10,000 samples).<br>Rear-panel switch sets polarity of<br>LAST SAMPLE before it is added<br>to the average. Can also be used to<br>invert polarity of average output. In<br>TOGGLE position, every other |

| Manual trigger                                                 | The unit will trigger if trigger<br>threshold is scanned through 0 VDC                                                                                                                                                             |                                           | sample is subtracted from the average. By triggering at twice the                                                                                                                                                           |

| Trigger LED                                                    | LED blinks with each trigger.                                                                                                                                                                                                      |                                           | experiment's rep rate, baseline will<br>be sampled on alternate triggers and                                                                                                                                                |

| Delay                                                          |                                                                                                                                                                                                                                    | Toggle output                             | subtracted from the average.<br>Rear-panel TTL signal changes state                                                                                                                                                         |

| Delay scale<br>Delay multiplier<br>Insertion delay<br>Accuracy | 1 ns to 10 ms<br>0 to 10× using 10-turn dial<br>25 ns<br>2 ns or 5 % of full-scale delay,                                                                                                                                          |                                           | with each trigger. Output used with<br>Active Baseline Subtraction feature<br>to indicate if next sample will be<br>added to, or subtracted from, the                                                                       |

| Jitter                                                         | whichever is larger<br><20 ps or 0.01 % of full-scale delay,                                                                                                                                                                       |                                           | moving average. Toggle output can drive 50 $\Omega$ loads to +2 VDC.                                                                                                                                                        |

| Ext. delay control                                             | whichever is larger<br>Rear-panel 0 to 10 VDC input over-<br>rides front-panel delay multiplier.                                                                                                                                   | Reset button<br>Remote reset              | Resets average to zero<br>Rear-panel input resets average with<br>a TTL low or switch closure.                                                                                                                              |

|                                                                | Input is used by SR200 or SR245 to scan the gate.                                                                                                                                                                                  | Signal Input and Ou                       | tput                                                                                                                                                                                                                        |

| Gate Width                                                     |                                                                                                                                                                                                                                    | Signal input                              | 1 M $\Omega$ input impedance, ±2 VDC usable range, protected to 100 VDC.                                                                                                                                                    |

| Width scale<br>Width multiplier<br>Width accuracy              | 1, 3, 10, 30, 100, 300 ns, 1, 3 μs<br>Adjustable from 1× to 5×<br>2 ns or 20 % of full scale,                                                                                                                                      |                                           | Input offset drift <0.5 mV/hr. after<br>20 min. warm-up. Shot noise at<br>input <0.5 mV. Coherent pickup                                                                                                                    |

| Minimum width                                                  | whichever is greater<br>2 ns, FWHM                                                                                                                                                                                                 | Signal output                             | <5 mV (easily cancelled with offset<br>knob in fixed gate applications).                                                                                                                                                    |

| Signal                                                         |                                                                                                                                                                                                                                    | Signal output                             | SIGNAL OUTPUT is the input<br>signal delayed by 3.5 ns. (Used to<br>terminate input signal and to time                                                                                                                      |

| Sensitivity (V <sub>in</sub> /V <sub>out</sub> )<br>Accuracy   | 1  V/1 V to 5 mV/1 V in a 1-2-5 seq.<br>3 % for gate widths >10 ns,<br>decreasing to 50 % for a 2 ns gate                                                                                                                          | Gate and Busy Outp                        | gate with respect to signal output.)                                                                                                                                                                                        |

| Filter                                                         | DC coupled, AC coupled above                                                                                                                                                                                                       | · · ·                                     |                                                                                                                                                                                                                             |

| Offset control<br>Over range LED                               | 10 Hz or AC coupled above 10 kHz<br>±0.4 VDC using 10-turn dial<br>Indicates input is >2 VDC or LAST                                                                                                                               | Gate output                               | 200 mV pulse marks exact position<br>of gate with respect to signal output.<br>$\pm 1$ ns accuracy (50 $\Omega$ load).                                                                                                      |

|                                                                | SAMPLE is greater than 10 VDC                                                                                                                                                                                                      | Busy output                               | TTL signal indicates output data is ready. High from trigger signal until                                                                                                                                                   |

| Last Sample                                                    |                                                                                                                                                                                                                                    |                                           | unit is ready for next trigger (45 µs min., longer for long delays or gate                                                                                                                                                  |

| Output                                                         | $\pm 10$ VDC, 10 mA (20 mA short circuit limit), impedance <1 $\Omega$                                                                                                                                                             |                                           | widths). Drives 50 $\Omega$ load to 2 VDC.                                                                                                                                                                                  |

| Polarity switch<br>Responsivity                                | Inverts LAST SAMPLE output<br>95 % (no more than 5 % of the                                                                                                                                                                        | General                                   |                                                                                                                                                                                                                             |

| •                                                              | previous last sample remains)                                                                                                                                                                                                      | Power supplies                            | +24 V/135 mA, +12 V/380 mA,<br>-12 V/230 mA, -24 V/150 mA.                                                                                                                                                                  |

| Averaging                                                      |                                                                                                                                                                                                                                    |                                           | 14 W. Power from a standard NIM crate (SR280).                                                                                                                                                                              |

| Type<br>Number of samples                                      | Exponential moving average 1, 3, 10, 30, to 10,000                                                                                                                                                                                 | Mechanical                                | Dual-width NIM enclosure<br>per TID20893                                                                                                                                                                                    |

| Average output                                                 | LAST is selected for no averaging $\pm 10$ VDC full scale, 10 mA (20 mA                                                                                                                                                            | Dimensions<br>Warranty                    | $2.7" \times 8.174" \times 11.5"$ (WHD)<br>One year parts and labor                                                                                                                                                         |

|                                                                |                                                                                                                                                                                                                                    |                                           |                                                                                                                                                                                                                             |

| SRS Stanford                                                   | d Research Systems                                                                                                                                                                                                                 |                                           | phone: (408)744-9040                                                                                                                                                                                                        |

|                                                                | •                                                                                                                                                                                                                                  |                                           | www.thinkCDC.com                                                                                                                                                                                                            |

## **Boxcar Sample Application**

Experiment Setup

This section describes a specific application of the SR250 Gated Integrator working together with other Boxcar system modules. Although the specific examples involve data acquisition in a pulsed laser experiment, many of the concepts and techniques are applicable to other areas.

## **Pulsed Laser Data Acquisition**

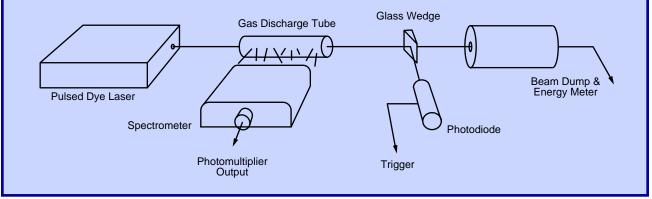

In this example, excited-state atoms in a gas discharge are to be transferred to a different excited state by a pulsed dye laser. The experimental arrangement is shown below. A pulsed dye laser is injected into a gas discharge tube which contains atoms in the initial excited state. A portion of the laser beam is split off and detected by a photodiode in order to trigger the gated integrator. The remainder of the beam is dumped to an energy meter which outputs a signal proportional to the energy in the laser pulse.

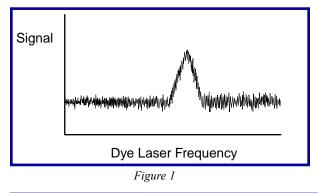

The transfer of population will be inferred by the increased fluorescence from the final state as the dye laser frequency is tuned through the transition frequency. The experiment is difficult because the background fluorescence signal from final-state atoms excited by the discharge is larger than the laser induced signal. A monochromater with a photomultiplier detects the signal at the wavelength of the final state. As the

laser wavelength is tuned, we'd like to see the signal from the photomultiplier look something like the representation in figure 1.

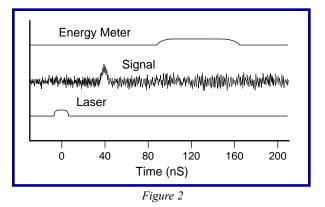

Some other aspects of the experiment can be inferred from the timing diagram below (figure 2):

1) The laser pulse width is about 8 ns.

2) There is a 40 ns delay in the photomultiplier, from the time photons strike the photo-cathode until the anode signal is seen.3) The laser induced signal is expected to be only 25 % of the background and is only present during the laser pulse. The experimenter wants a final signal-to-noise ratio of 5:1.

The boxcar system components needed for this measurement are shown on the next page. One SR250 is used to look at the output of the photomultiplier tube. To maximize the signal-tonoise ratio, we'd obviously like this integrator to be gated only during the time the signal is present. If we make the gate too wide, we'll be simply integrating more background without any more signal. That's why it's so important to use a gated integrator with low gate jitter such as the SR250. To ensure

proper gate timing, two equal lengths of cable can be brought from the signal output and the gate output to a dual-channel oscilloscope. By overlaying the traces, or by using the ADD mode of the scope, the gate can be accurately placed on top of the signal. This first SR250 will be triggered by a photodiode looking at a small reflection of the laser pulse. By triggering with the laser pulse itself, any jitter between the laser and the laser's own trigger can be ignored.

Since the signal is only 25 % of the background, and the desired final signal-to-noise ratio is 5:1, a 20 fold improvement in signal-to-noise is required. This can be accomplished by averaging over 400 shots. If the laser was firing at 10 Hz, this means that you'd have to wait at least 40 seconds at each point to get a valid measurement—if you scanned through the transition at a faster rate the data would be distorted.

A second SR250 in this experiment is integrating the signal from the energy meter. It is triggered by the busy output of the first boxcar, and will use a much longer gate. The averaging for the second SR250 should be the same as for the first.

We now have two boxcar outputs: one proportional to the signal intensity and one proportional to the laser intensity. Since we expect the signal to be proportional to the laser intensity, the effects of fluctuation and drifts in laser intensity can be removed by normalizing the signal to the laser intensity. This is done in our setup using the SR235 Analog Processor module. The averaged output of the signal SR250 is fed to the A input of the SR235. The averaged output of the laser intensity SR250 is sent to the B input. The SR235 is set

to output the value of 10A/B, or ln(A/B) if additional dynamic range is required. The output of the SR235 is displayed on a strip chart recorder.

## **Notes on Computer Interfacing**

Several improvements in the operation of this experiment can be achieved by controlling the data acquisition with a laboratory computer. The unique ability of the SR250 Gated Integrator module to provide shot-by-shot data dramatically enhances the instrument's utility in a computer controlled environment. Since the computer can acquire data on each laser shot, you are no longer limited to the exponential averaging provided by the SR250. For instance, the computer could be programmed to take 10 points at each wavelength and linearly average the results. Of course, we discussed earlier that averaging over 400 points was necessary to achieve the desired signal-to-noise improvement. In a computer controlled experiment we could take 10 points at each wavelength, and then average 40 entire scans together. In this manner, the effects of drift in laser intensity would be balanced over each scan instead of concentrated at the end of a single long scan.

The SR245 Computer Interface module is designed to work with the SR250 to bring you the advantages of computer control. The SR245 can be triggered by the SR250's "BUSY" output and acquire up to eight channels of analog data. The results can be sent back to your computer via RS-232 or GPIB interfaces.